随着计算机网络技术的发展,作为全球最大计算机网络—— I n t e r ac t 已成为当今信息社会重要的基础信息设施.在工业测控、智能仪器、智能家庭等领域,大量应用嵌入式设备接人 I n t e r n e t 的需求使得嵌入式 I n t e r ac t 技术日益成为研究的热点.嵌入式设备接人 I n t e r n e t 的关键是如何在硬件资源有限的嵌入式设备中实现 T C P / I P协议簇.实现复杂的 T C P / I P协议会占用其大量重要资源,这必然会影响嵌入式设备的性能,增加系统设计的复杂性和成本. Wl Z n e t 公司推出的系列硬件协议栈芯片—— W5 1 0 0网络接口芯片 ——为嵌入式设备接入 I n t e r n e t 提供了一种很好的解决方案.这种网络接口芯片可以使嵌入式设备在占用极低系统资源的条件下快速完成网络通讯. WI Z n e t 公司是一家专注于全硬接线 T C P / I P 核心技术的无晶圆厂半导体公司.目前, WI Z n e t 公司推出的系列硬件协议栈芯片有 W3 I O O A — L F , W3 1 5 0 A, W3 1 5 0 A +,W5 1 0 0,W5 3 0 0 .其中, W5 1 0 0是 W3 1 5 0 A的升级版本,它在 W3 1 5 0 A的基础上增加了一个以太网 P H Y,利用逻辑硬件实现,使系统设计更加简单、紧凑.W5 1 0 0是一款多功能的单片网络接口芯片,主要应用于高集成、高稳定、高性能和低成本的嵌入式系统中.本文主要介绍W5 1 0 0芯片的内部结构、工作原理、应用设计,并列举了一个实用实例.

1 W5 1 O 0芯片介绍

由于 W3 1 5 0 A使用时需要在外面接一个以太网物理层接口器件( R T L 8 2 0 1 C P ) ,增加了使用时的硬件难度¨引,因此 Wl Z n e t 公司最新推出了 W5 1 0 0,它是在 W3 1 5 0 A+的基础上,集成了以太网物理层 R T L 8 2 0 1 C P核,将 T C P / I P协议栈、以太网的 M A C和 P H Y的 3种功能集于一体. W5 1 0 0不仅保留了原来与 MC U接口的并行总线接口,还增加了 S P I串行总线接口. W5 1 0 0将 1 0 / 1 0 0 Mb p s以太网MA C和 P H Y集成到自动 M D I X,具有 1 6 k B数据缓冲区,线路传输率可达2 5 Mb p s .此外,它最大的特点是除了支持 T C P , A R P , I C M P等硬件协议栈外,还支持 P P P O E协议,不需要经过电脑就能直接接人 A D S L ,以实现数据通信。W5 1 0 0可以用于要求高通信速率的地方,如机顶盒、数字录像机、以太网络、远程控制器等. W5 1 0 0 “ 3合 1 ”的功能可以满足各种单片机在没有操作系统的支持下接人 I n t e r ac t ,而且操作简单、可靠,价格低廉,已被广泛应用于各种安全监测、音视频传输、远程信息传输等领域.

1 .1 芯片管脚分布与功能

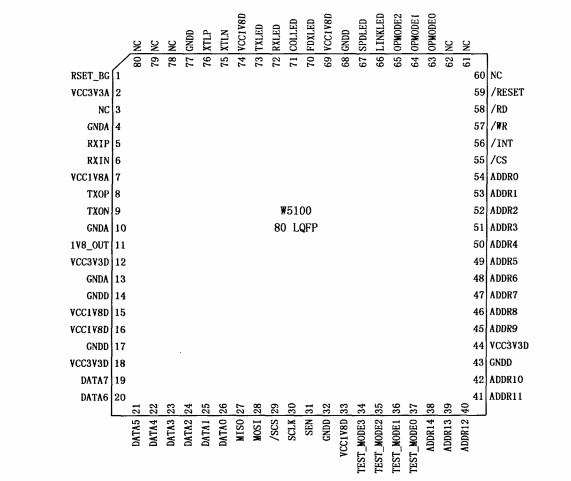

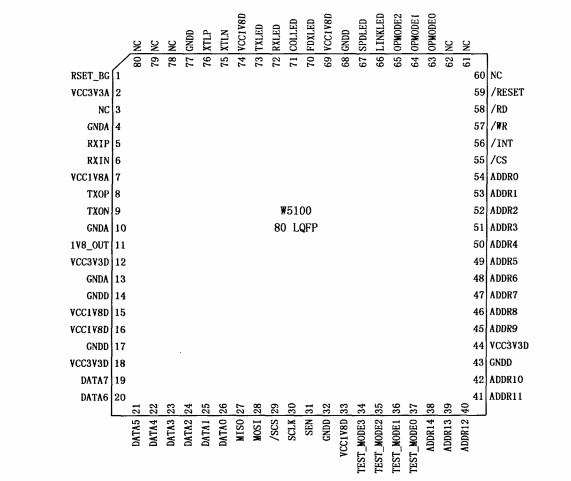

W5 1 0 0引脚分布如图 1 所示.

W5 1 0 0有 8 0个管脚,采用 L Q F P封装方式,按照功能可以将其分为以下 6类.

1 .1.1 MC U接口类管脚

与微处理器接口类管脚有3 3个,包括4种.

( 1 ) 地址总线引脚( 1 5个) A D D R[ 1 4~ 0] 分别对应 3 8— 4 2和4 5— 5 4管脚,这些引脚用来选择寄存器或存储器.在 W5 1 0 0与 M C U间采用总线方式通信时,要利用这些地址总线.

( 2 ) 数据总线引脚( 8个) D A T A[ 7~0 ] 分别对应管脚 l 9~ 2 6,这些引脚用来向W5 1 0 0内部读写数据.

( 3 ) 控制总线引脚 ( 5个) / R E S E T为 5 9脚,作为对 W5 1 0 0芯片进行初始化的引脚,低电平有效;/ C S为5 5脚,作为对 W5 1 0 0芯片进行片选的引脚,低电平有效;/ I N T为5 6脚,是中断输出引脚,当W5 1 0 0内部有中断发生时,该引脚输出低电平;/ WR,/ R D为5 7和5 8引脚,是读写控制信号,在向W5 1 0 0内部读写数据时由 MC U发出控制信号.

( 4 ) S P I 接口引脚( 5个) S E N为 3 O脚, S P I 接口使能引脚,使该引脚为低电平,则 S P I 模式禁止,否则有效; S C L K为2 9 脚, S P I 时钟输入;/ S C S为2 8脚, S P I 从模式选择,低电平有效; MO S I 为2 7脚, S P I 主出从人数据线引脚; MI S O为 2 6脚,主人从出数据线引脚。

1 .1.2 以太网物理层管脚

共有 8个管脚,包括以下4种.

( 1 ) 输入差分信号线对引脚( 2个) R X I P为 5 脚,是信号线对的正极管脚; R X I N为6脚,是信号线对的负极管脚.

( 2 ) 输出差分信号线对引脚( 2个) R X O 为 8脚,是信号线对的正极管脚; R XO N为 9脚,是信号线对的负极管脚.

( 3 ) 运行控制模式引脚( 3个) O P MO D E [ 2—0 ] 为 6 5— 6 3引脚,向3个引脚输人不同的信号,以太网物理层将工作在不同的模式下.如: 0 0 0为自动握手, 0 0 1为 1 0 0 B A S E — T X F D S / HD X自动握手等,其余模式参见参考文献[ 1 ] .

( 4 ) 其他( 1 个) R S E T — B G为 1 脚,该引脚需要对地外接一个 1 2 . 3 k Q、误差 1 %的电阻.

1.1.3 时钟信号管脚

X T L P为7 6脚, X T L N为 7 5脚,用来外接 2 5MHz的晶振.

1.1.4 工作状态 L E D灯信号管脚

工作状态 L E D灯信号管脚共 6个. W5 1 0 0芯片的6 6 , 6 7 , 7 O~7 3引脚分别输出连接、连接速度、双工模式、 I P地址冲突、接收,以及发送状态信号,分别连接一个 L E D灯显示,低电平有效.

1.1.5 电源管脚

W5 1 0 0芯片有 3 .3 V和 1.8 V两种工作电压,其中1.8V由芯片内部产生, 3.3V电源由外部电路提供.

1.1.6 其他管脚

( 1 ) 模式选择引脚 ( 4个) T E S T — M O D E[ 3~0 ] 为 3 4~3 7共 4个引脚, W5 1 0 0模式选择,0 0 0 0为通用模式,其他作内部测试.

1.2 W5 1 0 0内部结构

W5 1 0 0的内部结构如图2所示.其芯片主要由4部分组成,即:硬件 T C P / I P内核;微控器MC U接口单元;发送/接收数据缓冲区;以太网物理层单元.

W5 1 0 0内含公共寄存器、端口寄存器、发送和接收数据缓存器,占用 3 2 k B的存储器地址空间.其中, O x O 0 0 0~O x 0 0 2 F单元为公共寄存器,O x 0 4 0 0一O x 0 7 F F单元为端口寄存器, O x 4 0 0 0一O x 5 F F F单元为发送存储器, O x 6 0 0 0一O x 7 F F F单元为接收存储器,其余为保留区域.

1.2.1 公共寄存器

公共寄存器主要包括模式寄存器 ( M R) 、网关地址寄存器 ( G WR) 、子网掩码寄存器( S U B R) 、本机硬件地址寄存器( S H A R) 、本机 I P地址寄存器 ( S I P R) 、中断寄存器 ( I R) 、中断屏蔽寄存器( I MR) 、重试时间寄存器( R T R ) 、重试次数寄存器( R C R) 、接收数据缓冲区大小寄存器( R MS R) ,以及发送数据缓冲区大小寄存器( T MS R) 等.

( 1 ) 本机配置寄存器包括 S I P R, S U B R, S H A R, G WR等 4个寄存器,主要用于存放本机的I P地址、子网掩码、硬件地址,以及网关 I P .WS 1 0 0在进行通信前,要事先对这些寄存器进行配置.

( 2 ) 中断相关寄存器包括 I R和 I MR寄存器. I R的 D 。~D 中,除 D 外的 7位分别为W5 1 0 0的7个中断源标志位.

D 0-D 3为 W5 1 0 0的 4个端口的中断标志位, S o c k e t发生中断时,产生置位.第 5位显示P P P O E连接是否结束,如果结束,该位置为 1 ;第6位为目标未可连接的显示位;第7位为 I P产生冲突时的显示位. 5 , 6 , 7位都可通过对该位写“ 1 ”实现自动清零.任何中断位都可以被 I MR中的位屏蔽.

( 3 ) 数据缓冲区设置寄存器包括 R M S R和T MS R寄存器,主要设置接收/发送数据缓冲区的大小. 接收/发送数据缓冲区各共有 8 k ,通过对R MS R和T MS R的设置,可以灵活分配4个通道的缓冲区大小.

1.2.2 端口寄存器

端口寄存器主要用于网络连接后控制各个通路的数据收发. W5 1 0 0支持 4条通路,与其对应的有完全等价的4套接字寄存器,即Sn =S0 , S1 , S2 , S3 .通道均有一套独立的寄存器设置.

( 1 ) 端口命令寄存器( Sn _ C R ) 主要用于控制相应端口的初始化、关断,以及建立连接和终止、数据传输、命令接收.对该位写入相应的数值,即可实现不同的控制.

( 2 ) 端口中断寄存器( Sn_I R) 主要用于通报通路连接情况, Sn_ I R的 D0-D4 分别对应连接、断开、接收、超时、发送成功等操作状态.

( 3 ) 端口状态寄存器( Sn_S R) 用于显示相应端口的各种状况.例如,设 Sn_S R初始状态为SOCK— C L O S E D,当命令寄存器被置为 L I S T E N 时,而 S o c k e t ( n ) 被置为 T C P服务器模式且正常建立连接.此时, Sn_ S R= S O C K — L I S T E N;当命令寄存器被置为 O P E N,模式为 U D P时,则 Sn_S R=S o c k — UDP.

2 W5 1 0 0应用实例

2.1 单片机与 W5 1 0 0接口设计

本文以A T 8 9 S 5 1 单片机为微控制器,简要介绍 W5 1 0 0芯片的应用设计.采用总线接口方式,以提高数据的传输速率,且方便接口.总线接口方式需要单片机提供较多的 I / O 线,但连接方法简单,只需要 W5 1 0 0芯片的地址总线、数据总线和控制总线与单片机 A T 8 9 S 5 1的相应总线对应连接即可.

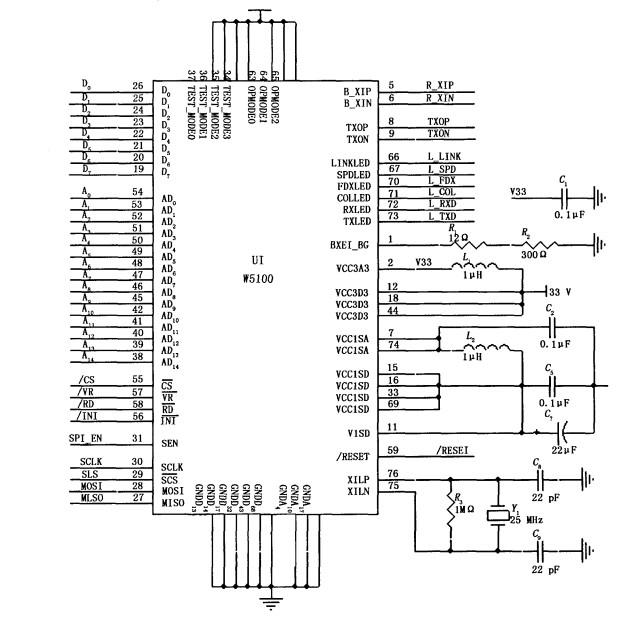

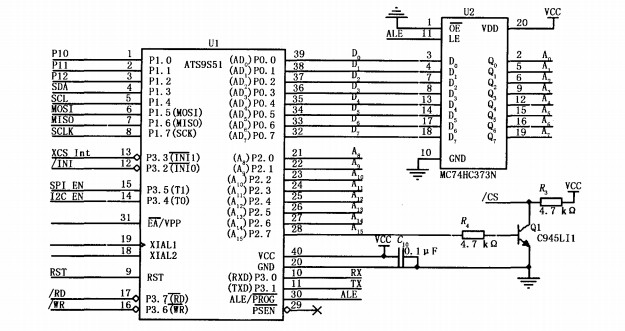

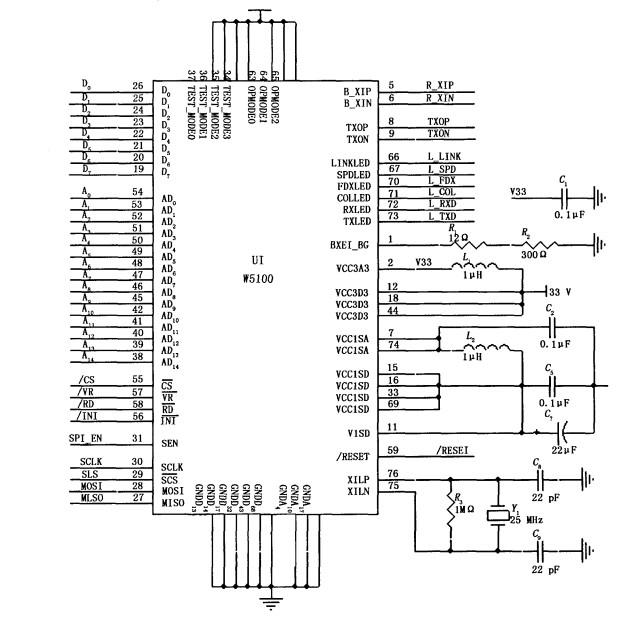

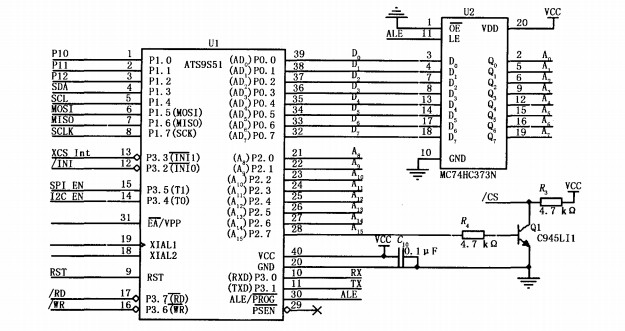

图3是 W5 1 0 0芯片的外围连接电路.图4是A T 8 9 S 5 1单片机控制电路.地址总线为 A15 ~0, 其中 A14 ~A0 连接 W5 1 0 0芯片地址总线 A14 ~ A 0 , A15 连接 W5 1 0 0芯片的/ C S脚.因此, W5 1 0 0芯片的地址是 0 0 0 0 H~ 7 F F F H.单片机可以通过其总线结构方便地访问 W5 1 0 0芯片内部的所有寄存器.由于W5 1 0 0芯片内部集成了以太网物理层单元,因此可以省去 W3 1 0 0 A芯片应用电路中如 R T L 8 2 0等的以太网物理层芯片,以简化电路,节约成本,提高电路的可靠性。

2.2 W5 1 0 0通信程序设计

要利用 W5 1 0 0模块实现数据在因特网中的传输,需要编写单片机控制程序. A T 8 9 $ 5 1单片机程序可以采用汇编语言或者 C语言. C语言的主要处理程序如下.

( 1 ) 初始化 i n i t W5 1 0 0 A 0 //初始化 W5 1 0 0 ,设置各个接受/发送数据缓冲区的大小;s e t g a t e w a y ( i p ) //设置网关; s e t M A C A d d r ( i p ) //设置物理地址; s e t s u b ma s t ( i p ) //设置子网掩码; s e t l P ( i p ) //设置 l P地址; s e t R C R( t i m e ) //设置超时时间; i n i t — s o c k( i , I p o r t , f l a g , 0 , Sn_MR_T C P ) //初始化各个套接字.

( 2 ) 连接 s o c k e t ( i , S 一MR _ T C P , l o c a l - -p o r t +l n c+ +, 0) //设置 T C P方式, C l i e n t端口;c o n n e c t ( i , i p , p o r t) //连接设定了 I P和端口的服务器.

( 3 ) 数据发送和传输 r e c v ( i , r x — b u f , l e n ) //S o c k e t ( i ) 接收l e n长度的数据,存放于 I X — b u f 中;s e n d ( i , t x — b u f , l e n ) // S o c k e t ( i ) 通过 t x — b u f 发送l e n长度的数据.

3 结 语

W5 1 0 0芯片的推出,大大简化了硬件电路设计,使单片机系统在没有操作系统支持下,真正使单芯片接人 I n t e r ac t 成为现实. W5 l O 0在以往的网络接口芯片基础上,将 T C P / I P协议栈、以太网MA C和 P H Y集成在一块芯片上,大大简化了硬件设计难度.而且通过内部嵌入硬件协议栈,省去了传统繁琐的以太网协议编写和调试步骤,加快了系统开发速度,因此该芯片应用前景良好.

文/王计元 ( 上海电力学院计算机与信息工程学院)

1 W5 1 O 0芯片介绍

由于 W3 1 5 0 A使用时需要在外面接一个以太网物理层接口器件( R T L 8 2 0 1 C P ) ,增加了使用时的硬件难度¨引,因此 Wl Z n e t 公司最新推出了 W5 1 0 0,它是在 W3 1 5 0 A+的基础上,集成了以太网物理层 R T L 8 2 0 1 C P核,将 T C P / I P协议栈、以太网的 M A C和 P H Y的 3种功能集于一体. W5 1 0 0不仅保留了原来与 MC U接口的并行总线接口,还增加了 S P I串行总线接口. W5 1 0 0将 1 0 / 1 0 0 Mb p s以太网MA C和 P H Y集成到自动 M D I X,具有 1 6 k B数据缓冲区,线路传输率可达2 5 Mb p s .此外,它最大的特点是除了支持 T C P , A R P , I C M P等硬件协议栈外,还支持 P P P O E协议,不需要经过电脑就能直接接人 A D S L ,以实现数据通信。W5 1 0 0可以用于要求高通信速率的地方,如机顶盒、数字录像机、以太网络、远程控制器等. W5 1 0 0 “ 3合 1 ”的功能可以满足各种单片机在没有操作系统的支持下接人 I n t e r ac t ,而且操作简单、可靠,价格低廉,已被广泛应用于各种安全监测、音视频传输、远程信息传输等领域.

1 .1 芯片管脚分布与功能

W5 1 0 0引脚分布如图 1 所示.

W5 1 0 0有 8 0个管脚,采用 L Q F P封装方式,按照功能可以将其分为以下 6类.

1 .1.1 MC U接口类管脚

与微处理器接口类管脚有3 3个,包括4种.

( 1 ) 地址总线引脚( 1 5个) A D D R[ 1 4~ 0] 分别对应 3 8— 4 2和4 5— 5 4管脚,这些引脚用来选择寄存器或存储器.在 W5 1 0 0与 M C U间采用总线方式通信时,要利用这些地址总线.

( 2 ) 数据总线引脚( 8个) D A T A[ 7~0 ] 分别对应管脚 l 9~ 2 6,这些引脚用来向W5 1 0 0内部读写数据.

( 3 ) 控制总线引脚 ( 5个) / R E S E T为 5 9脚,作为对 W5 1 0 0芯片进行初始化的引脚,低电平有效;/ C S为5 5脚,作为对 W5 1 0 0芯片进行片选的引脚,低电平有效;/ I N T为5 6脚,是中断输出引脚,当W5 1 0 0内部有中断发生时,该引脚输出低电平;/ WR,/ R D为5 7和5 8引脚,是读写控制信号,在向W5 1 0 0内部读写数据时由 MC U发出控制信号.

( 4 ) S P I 接口引脚( 5个) S E N为 3 O脚, S P I 接口使能引脚,使该引脚为低电平,则 S P I 模式禁止,否则有效; S C L K为2 9 脚, S P I 时钟输入;/ S C S为2 8脚, S P I 从模式选择,低电平有效; MO S I 为2 7脚, S P I 主出从人数据线引脚; MI S O为 2 6脚,主人从出数据线引脚。

1 .1.2 以太网物理层管脚

共有 8个管脚,包括以下4种.

( 1 ) 输入差分信号线对引脚( 2个) R X I P为 5 脚,是信号线对的正极管脚; R X I N为6脚,是信号线对的负极管脚.

( 2 ) 输出差分信号线对引脚( 2个) R X O 为 8脚,是信号线对的正极管脚; R XO N为 9脚,是信号线对的负极管脚.

( 3 ) 运行控制模式引脚( 3个) O P MO D E [ 2—0 ] 为 6 5— 6 3引脚,向3个引脚输人不同的信号,以太网物理层将工作在不同的模式下.如: 0 0 0为自动握手, 0 0 1为 1 0 0 B A S E — T X F D S / HD X自动握手等,其余模式参见参考文献[ 1 ] .

( 4 ) 其他( 1 个) R S E T — B G为 1 脚,该引脚需要对地外接一个 1 2 . 3 k Q、误差 1 %的电阻.

1.1.3 时钟信号管脚

X T L P为7 6脚, X T L N为 7 5脚,用来外接 2 5MHz的晶振.

1.1.4 工作状态 L E D灯信号管脚

工作状态 L E D灯信号管脚共 6个. W5 1 0 0芯片的6 6 , 6 7 , 7 O~7 3引脚分别输出连接、连接速度、双工模式、 I P地址冲突、接收,以及发送状态信号,分别连接一个 L E D灯显示,低电平有效.

1.1.5 电源管脚

W5 1 0 0芯片有 3 .3 V和 1.8 V两种工作电压,其中1.8V由芯片内部产生, 3.3V电源由外部电路提供.

1.1.6 其他管脚

( 1 ) 模式选择引脚 ( 4个) T E S T — M O D E[ 3~0 ] 为 3 4~3 7共 4个引脚, W5 1 0 0模式选择,0 0 0 0为通用模式,其他作内部测试.

图1 W5 1 0 0管脚分布

( 2 ) N C引脚( 7个) 主要有 3 , 6 0~6 2 , 7 8~8 O共 7个引脚供厂家测试之用。 1.2 W5 1 0 0内部结构

W5 1 0 0的内部结构如图2所示.其芯片主要由4部分组成,即:硬件 T C P / I P内核;微控器MC U接口单元;发送/接收数据缓冲区;以太网物理层单元.

W5 1 0 0内含公共寄存器、端口寄存器、发送和接收数据缓存器,占用 3 2 k B的存储器地址空间.其中, O x O 0 0 0~O x 0 0 2 F单元为公共寄存器,O x 0 4 0 0一O x 0 7 F F单元为端口寄存器, O x 4 0 0 0一O x 5 F F F单元为发送存储器, O x 6 0 0 0一O x 7 F F F单元为接收存储器,其余为保留区域.

1.2.1 公共寄存器

公共寄存器主要包括模式寄存器 ( M R) 、网关地址寄存器 ( G WR) 、子网掩码寄存器( S U B R) 、本机硬件地址寄存器( S H A R) 、本机 I P地址寄存器 ( S I P R) 、中断寄存器 ( I R) 、中断屏蔽寄存器( I MR) 、重试时间寄存器( R T R ) 、重试次数寄存器( R C R) 、接收数据缓冲区大小寄存器( R MS R) ,以及发送数据缓冲区大小寄存器( T MS R) 等.

图2 W5 1 0 0内部结构

( 1 ) 本机配置寄存器包括 S I P R, S U B R, S H A R, G WR等 4个寄存器,主要用于存放本机的I P地址、子网掩码、硬件地址,以及网关 I P .WS 1 0 0在进行通信前,要事先对这些寄存器进行配置.

( 2 ) 中断相关寄存器包括 I R和 I MR寄存器. I R的 D 。~D 中,除 D 外的 7位分别为W5 1 0 0的7个中断源标志位.

D 0-D 3为 W5 1 0 0的 4个端口的中断标志位, S o c k e t发生中断时,产生置位.第 5位显示P P P O E连接是否结束,如果结束,该位置为 1 ;第6位为目标未可连接的显示位;第7位为 I P产生冲突时的显示位. 5 , 6 , 7位都可通过对该位写“ 1 ”实现自动清零.任何中断位都可以被 I MR中的位屏蔽.

( 3 ) 数据缓冲区设置寄存器包括 R M S R和T MS R寄存器,主要设置接收/发送数据缓冲区的大小. 接收/发送数据缓冲区各共有 8 k ,通过对R MS R和T MS R的设置,可以灵活分配4个通道的缓冲区大小.

1.2.2 端口寄存器

端口寄存器主要用于网络连接后控制各个通路的数据收发. W5 1 0 0支持 4条通路,与其对应的有完全等价的4套接字寄存器,即Sn =S0 , S1 , S2 , S3 .通道均有一套独立的寄存器设置.

( 1 ) 端口命令寄存器( Sn _ C R ) 主要用于控制相应端口的初始化、关断,以及建立连接和终止、数据传输、命令接收.对该位写入相应的数值,即可实现不同的控制.

( 2 ) 端口中断寄存器( Sn_I R) 主要用于通报通路连接情况, Sn_ I R的 D0-D4 分别对应连接、断开、接收、超时、发送成功等操作状态.

( 3 ) 端口状态寄存器( Sn_S R) 用于显示相应端口的各种状况.例如,设 Sn_S R初始状态为SOCK— C L O S E D,当命令寄存器被置为 L I S T E N 时,而 S o c k e t ( n ) 被置为 T C P服务器模式且正常建立连接.此时, Sn_ S R= S O C K — L I S T E N;当命令寄存器被置为 O P E N,模式为 U D P时,则 Sn_S R=S o c k — UDP.

2 W5 1 0 0应用实例

2.1 单片机与 W5 1 0 0接口设计

本文以A T 8 9 S 5 1 单片机为微控制器,简要介绍 W5 1 0 0芯片的应用设计.采用总线接口方式,以提高数据的传输速率,且方便接口.总线接口方式需要单片机提供较多的 I / O 线,但连接方法简单,只需要 W5 1 0 0芯片的地址总线、数据总线和控制总线与单片机 A T 8 9 S 5 1的相应总线对应连接即可.

图3是 W5 1 0 0芯片的外围连接电路.图4是A T 8 9 S 5 1单片机控制电路.地址总线为 A15 ~0, 其中 A14 ~A0 连接 W5 1 0 0芯片地址总线 A14 ~ A 0 , A15 连接 W5 1 0 0芯片的/ C S脚.因此, W5 1 0 0芯片的地址是 0 0 0 0 H~ 7 F F F H.单片机可以通过其总线结构方便地访问 W5 1 0 0芯片内部的所有寄存器.由于W5 1 0 0芯片内部集成了以太网物理层单元,因此可以省去 W3 1 0 0 A芯片应用电路中如 R T L 8 2 0等的以太网物理层芯片,以简化电路,节约成本,提高电路的可靠性。

2.2 W5 1 0 0通信程序设计

要利用 W5 1 0 0模块实现数据在因特网中的传输,需要编写单片机控制程序. A T 8 9 $ 5 1单片机程序可以采用汇编语言或者 C语言. C语言的主要处理程序如下.

( 1 ) 初始化 i n i t W5 1 0 0 A 0 //初始化 W5 1 0 0 ,设置各个接受/发送数据缓冲区的大小;s e t g a t e w a y ( i p ) //设置网关; s e t M A C A d d r ( i p ) //设置物理地址; s e t s u b ma s t ( i p ) //设置子网掩码; s e t l P ( i p ) //设置 l P地址; s e t R C R( t i m e ) //设置超时时间; i n i t — s o c k( i , I p o r t , f l a g , 0 , Sn_MR_T C P ) //初始化各个套接字.

( 2 ) 连接 s o c k e t ( i , S 一MR _ T C P , l o c a l - -p o r t +l n c+ +, 0) //设置 T C P方式, C l i e n t端口;c o n n e c t ( i , i p , p o r t) //连接设定了 I P和端口的服务器.

( 3 ) 数据发送和传输 r e c v ( i , r x — b u f , l e n ) //S o c k e t ( i ) 接收l e n长度的数据,存放于 I X — b u f 中;s e n d ( i , t x — b u f , l e n ) // S o c k e t ( i ) 通过 t x — b u f 发送l e n长度的数据.

图 3 W5 1 0 0芯片外围电路

图4 单片机控制电路

3 结 语

W5 1 0 0芯片的推出,大大简化了硬件电路设计,使单片机系统在没有操作系统支持下,真正使单芯片接人 I n t e r ac t 成为现实. W5 l O 0在以往的网络接口芯片基础上,将 T C P / I P协议栈、以太网MA C和 P H Y集成在一块芯片上,大大简化了硬件设计难度.而且通过内部嵌入硬件协议栈,省去了传统繁琐的以太网协议编写和调试步骤,加快了系统开发速度,因此该芯片应用前景良好.

文/王计元 ( 上海电力学院计算机与信息工程学院)

没有评论:

发表评论